Paper Multirate Timestamp Modeling for Ultralow-Jitter Frequency Synthesis: A Tutorial

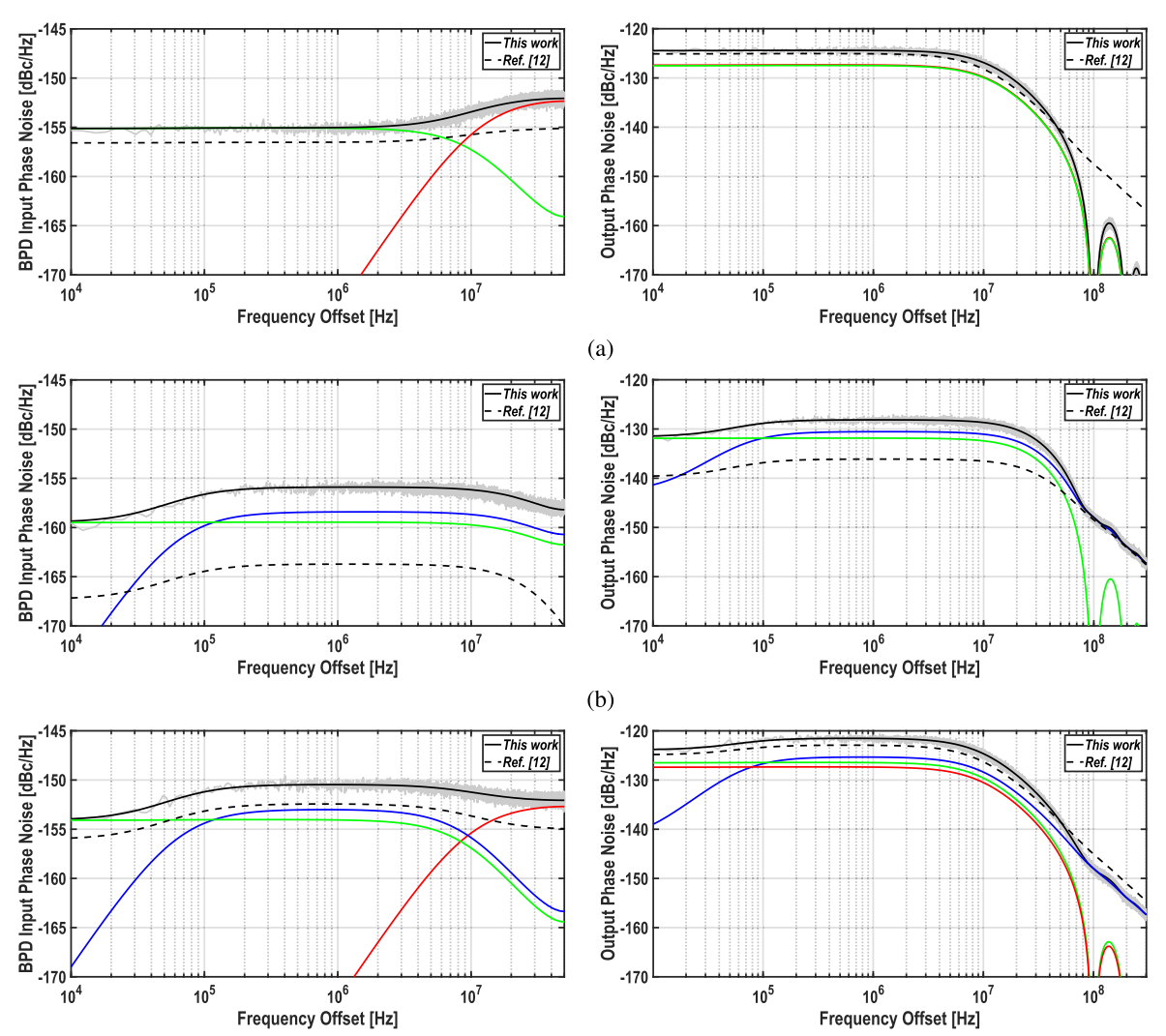

- High-bandwidth PLL (\(\ge 30 \% f_{ref}\)).

- ADPLL with TDC and digitial loop filter.

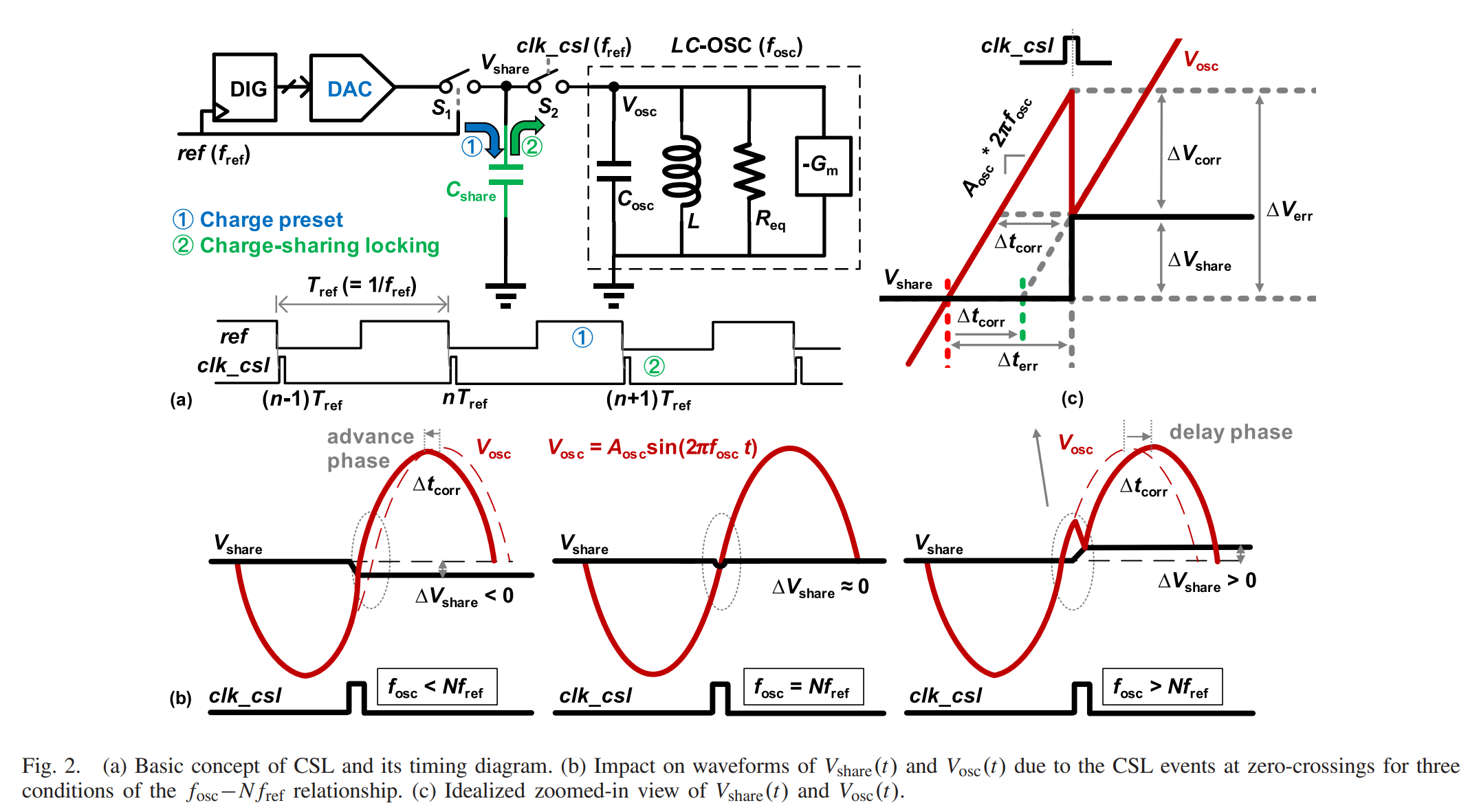

- Injection locking or charge-sharing locking oscillator.

(a) Conceptual multirate timestamp model suitable for a high-bandwidth PLL. (b) Implementation details of the ADPLL blocks (ADC-based TDC and digital loop filter) that convert \(\Delta t_{err}[n]\) into \(\Delta T_{corr}[n]\).

(a) Conceptual multirate timestamp model suitable for a high-bandwidth PLL. (b) Implementation details of the ADPLL blocks (ADC-based TDC and digital loop filter) that convert \(\Delta t_{err}[n]\) into \(\Delta T_{corr}[n]\).

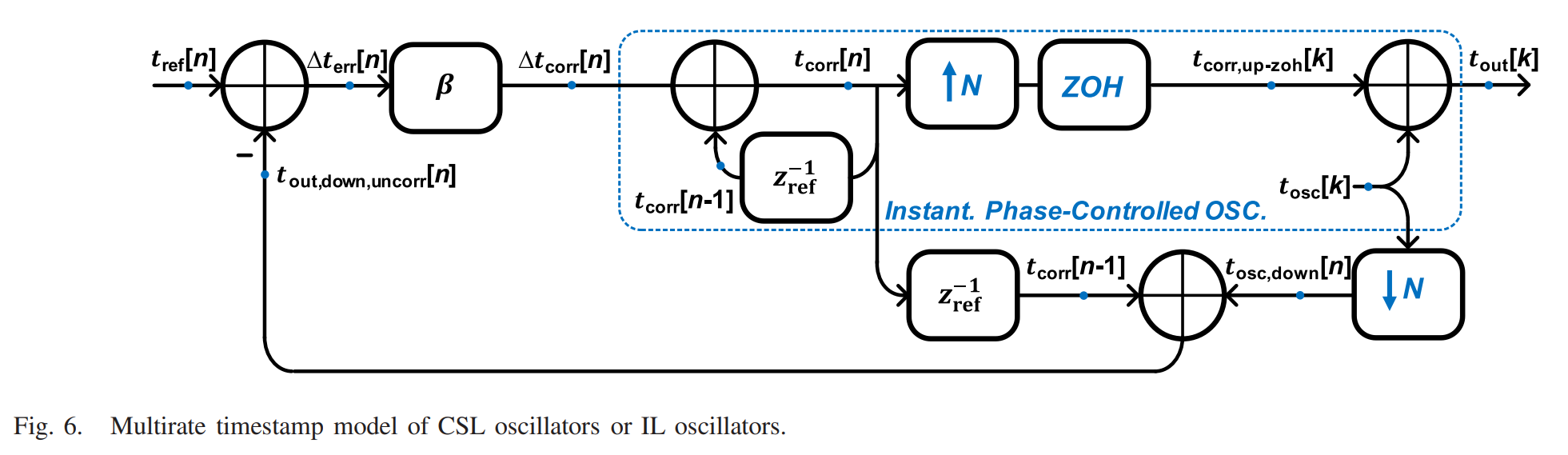

Multirate timestamp model of CSL or IL oscillators.

Multirate timestamp model of CSL or IL oscillators.

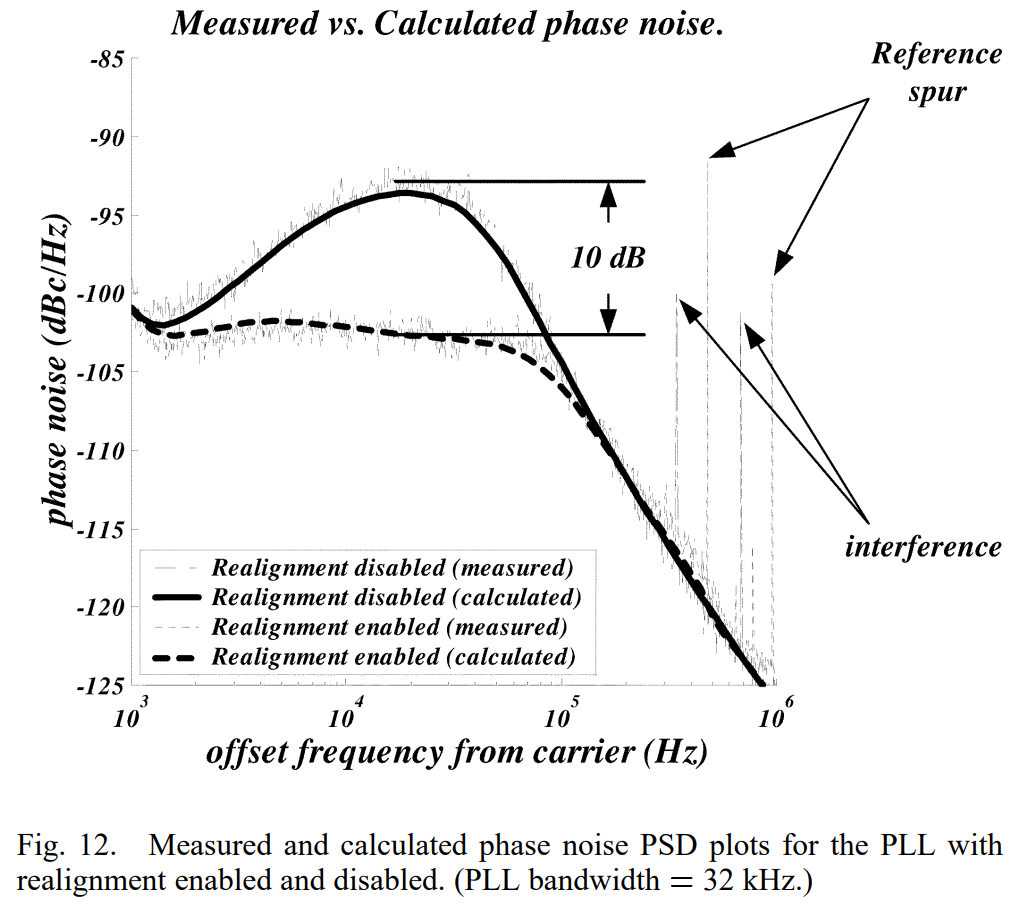

Paper A Comprehensive Phase Noise Analysis of Bang-Bang Digital PLLs

- Bang-bang DPLL.

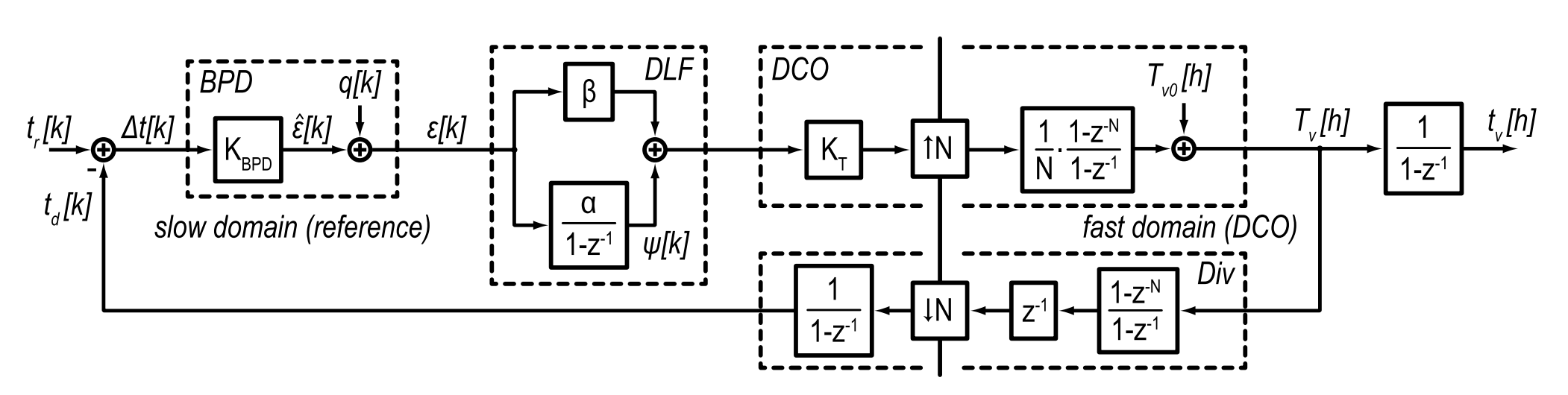

Bang-bang DPLL multirate time-domain model.

Bang-bang DPLL multirate time-domain model.

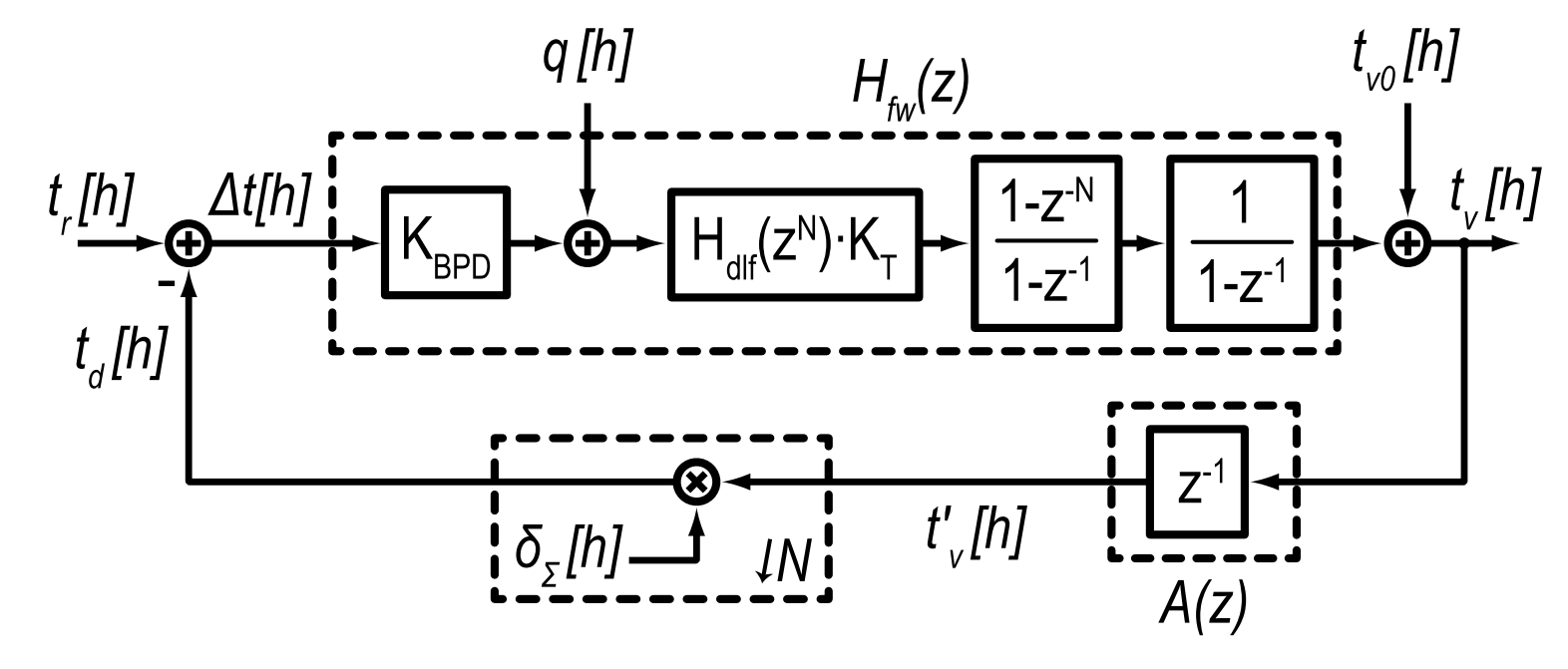

Linearized time-variant bang-bang DPLL model.

Linearized time-variant bang-bang DPLL model.

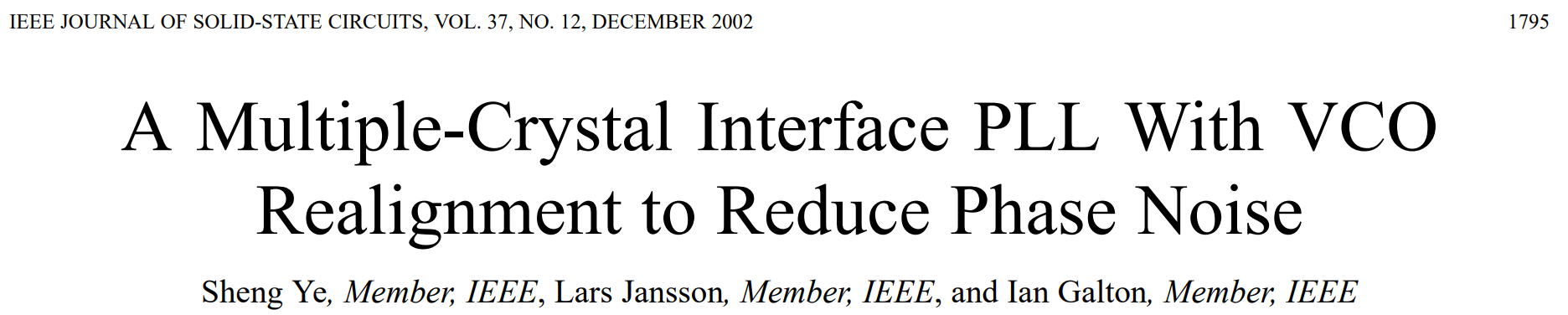

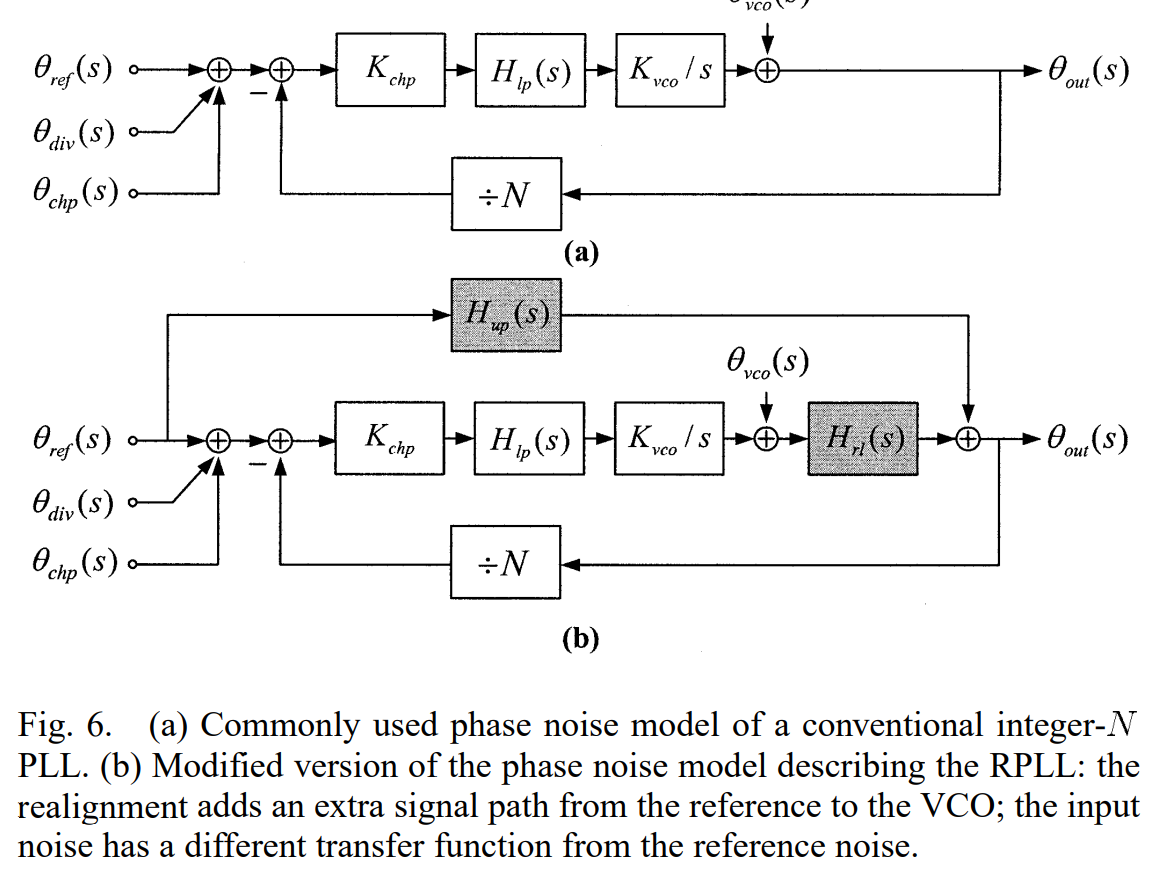

Paper A multiple-crystal interface PLL with VCO realignment to reduce phase noise

- Phase realignment (injection) PLL.

- MDLL

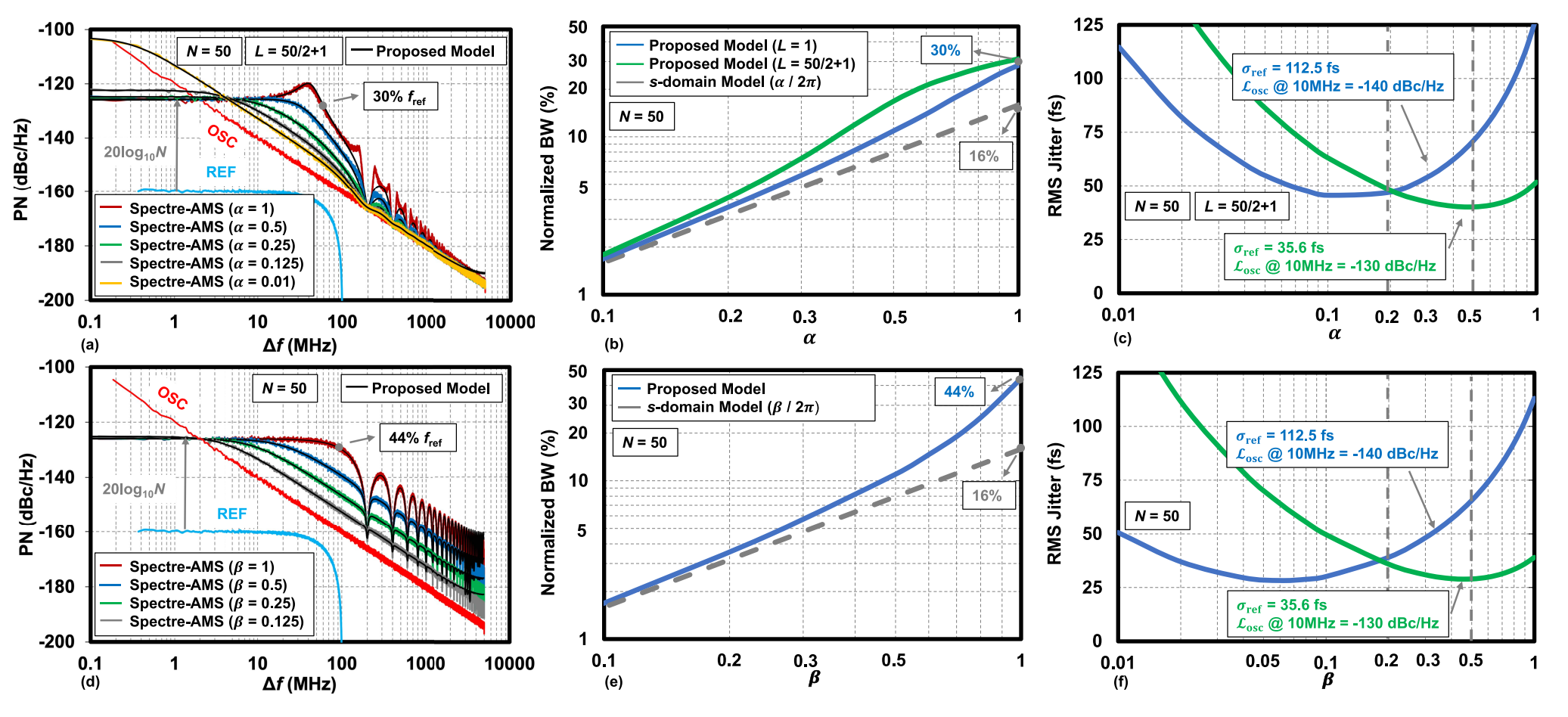

- It exhibits quite a good agreement when the frequency ratio \(N\) is large (e.g., \(N > 10\)) and the realigning factor (i.e., injection strength) \(\beta\) is small (e.g., \(\beta < 0.2\)), but it cannot predict the phase noise folding.

Paper A Charge-Sharing Locking Technique With a General Phase Noise Theory of Injection Locking